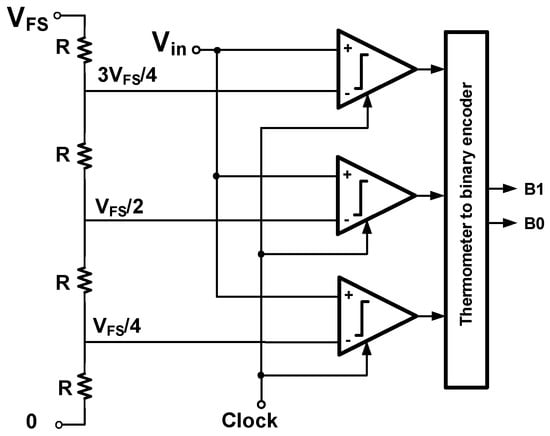

JLPEA | Free Full-Text | Review of Analog-To-Digital Conversion Characteristics and Design Considerations for the Creation of Power-Efficient Hybrid Data Converters

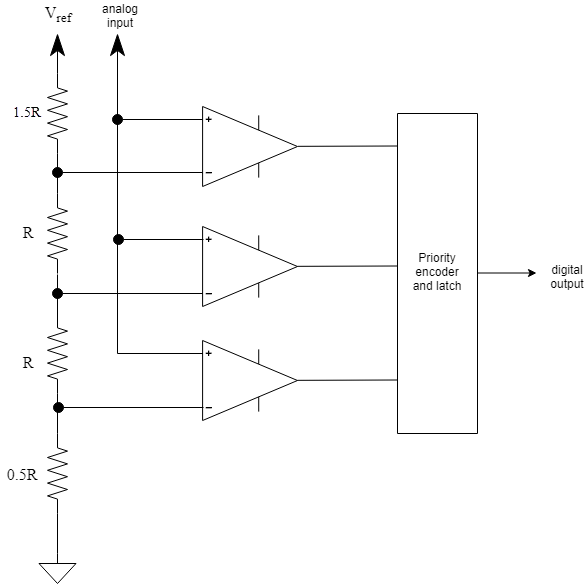

GitHub - muhammadaldacher/Modeling-of-4-bit-Flash-ADC-and-4-bit-DAC: This project shows how to model a 4-bit flash ADC and a 4-bit DAC using ideal components. Used vdc, vpulse, vcvs, switch, res, cap, vccs to construct the 4-bit